# Micro-Power Voltage Detector with Manual Reset

### **General Description**

The RT9807 is a micro-power voltage detector with deglitched manual reset input which supervises the power supply voltage level for microprocessors ( $\mu P$ ) or digital systems. It provides internally fixed threshold levels ranging from 1.2V to 3.3V with 0.1V per step, which covers most digital applications. It features low supply current of  $3\mu A$ .

The RT9807 performs supervisory function by sending out a reset signal whenever the VDD voltage falls below a preset threshold level. The timeout period of this reset signal can be adjusted via an external capacitor. Once VDD recovers above the threshold level, the reset signal will be released after a certain delay time. To manually pull reset signal low, just pull the manual reset input (MR) below the specified logic-low level.

The RT9807 is available in an SOT-23-5 package.

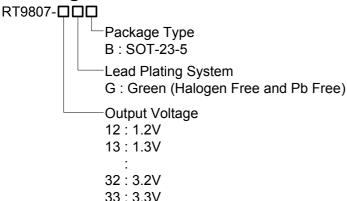

## **Ordering Information**

Richtek products are:

Note:

- ▶RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶Suitable for use in SnPb or Pb-free soldering processes.

## **Marking Information**

For marking information, contact our sales representative directly or through a Richtek distributor located in your area.

#### **Features**

- Monitor System Voltages from 0.9V to 5.5V

- Capacitor-Adjustable Reset Timeout Period

- Manual Reset Input

- Low Quiescent Current

- High Accuracy ±1.5%

- Low Functional Supply Voltage 0.9V

- N-Channel Open-Drain Output

- Small SOT-23-5 Package

- RoHS Compliant and Halogen Free

## **Applications**

- Computers

- Controllers

- Intelligent Instruments

- · Critical uP and uC Power Monitoring

- Portable/Battery-Powered Equipment

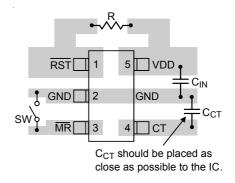

## **Pin Configurations**

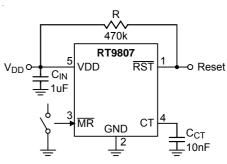

# **Typical Application Circuit**

DS9807-01 April 2011

# **Functional Pin Description**

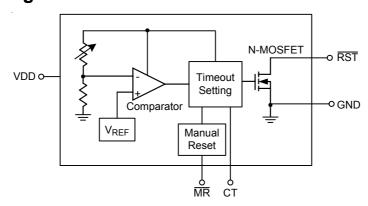

| Pin No. | Pin Name | Pin Function                                                    |  |  |

|---------|----------|-----------------------------------------------------------------|--|--|

| 1       | RST      | Reset Output Pin. (Open drain)                                  |  |  |

| 2       | GND      | Ground Pin.                                                     |  |  |

| 3       | MR       | Manual Reset Pin.                                               |  |  |

| 4       | СТ       | Connect an external capacitor for setting reset timeout period. |  |  |

| 5       | VDD      | Supply Voltage Input Pin.                                       |  |  |

# **Function Block Diagram**

# Absolute Maximum Ratings (Note 1)

| • Supply Input Voltage, V <sub>DD</sub>                     | 0.3V to 6V    |

|-------------------------------------------------------------|---------------|

| • Reset Output Voltage, RST                                 | 0.3V to 6V    |

| • Other Pins                                                | 0.3V to 6V    |

| • Power Dissipation, P <sub>D</sub> @ T <sub>A</sub> = 25°C |               |

| SOT-23-5                                                    | 0.4W          |

| Package Thermal Resistance (Note 2)                         |               |

| SOT-23-5, $\theta_{JA}$                                     | 250°C/W       |

| Junction Temperature Range                                  | 150°C         |

| • Lead Temperature (Soldering, 10 sec.)                     | 260°C         |

| Storage Temperature Range                                   | 65°C to 150°C |

| • ESD Susceptibility (Note 3)                               |               |

| HBM (Human Body Mode)                                       | 2kV           |

| MM (Machine Mode)                                           | 200V          |

|                                                             |               |

## **Recommended Operating Conditions** (Note 4)

| • Junction Temperature Range | 40°C to  | 125°C |

|------------------------------|----------|-------|

| • Ambient Temperature Range  | -40°C to | 85°C  |

### **Electrical Characteristics**

(T<sub>A</sub> = 25°C, unless otherwise specified)

| Parameter                       |                               | Symbol               | Test Conditions                                                     | Min                | Тур                  | Max                 | Unit   |

|---------------------------------|-------------------------------|----------------------|---------------------------------------------------------------------|--------------------|----------------------|---------------------|--------|

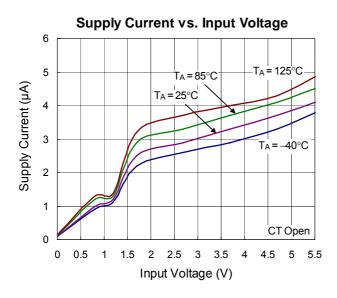

| Operating VDD Range             |                               | $V_{DD}$             |                                                                     | 0.9                |                      | 5.5                 | V      |

| Supply Current                  | Supply Current                |                      | V <sub>TH</sub> = 3V, V <sub>DD</sub> = 4.5V                        |                    | 3                    | 5                   | μА     |

| Reset Threshold                 | Reset Threshold               |                      |                                                                     | 1.2                |                      | 3.3                 | V      |

| Threshold Voltage               | Accuracy                      | $\Delta V_{TH}$      |                                                                     | -1.5               |                      | 1.5                 | %      |

| Threshold Voltage               | Threshold Voltage Hysteresis  |                      |                                                                     |                    | 50 x V <sub>TH</sub> |                     | mV     |

| Reset Threshold Tempco          |                               |                      |                                                                     |                    | 100                  |                     | ppm/°C |

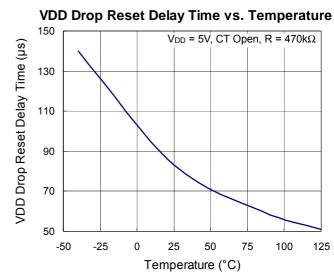

| VDD Drop to Reset Delay         |                               | t <sub>RP</sub>      | Drop = V <sub>TH</sub> – 250mV                                      |                    | 100                  |                     | μS     |

| RST Output Voltage Low (Note 5) |                               | V <sub>OL</sub>      | V <sub>DD</sub> < V <sub>TH(min.)</sub> , I <sub>SINK</sub> = 3.5mA |                    |                      | 0.4                 | V      |

| MR Input                        | Logic-High                    | V <sub>IH</sub>      |                                                                     | 0.7V <sub>DD</sub> |                      |                     | V      |

| Threshold voltage               | Logic-Low                     | VIL                  |                                                                     |                    |                      | 0.25V <sub>DD</sub> |        |

| MR Glitch Rejection             | MR Glitch Rejection           |                      |                                                                     |                    | 80                   |                     | ns     |

| MR to Reset Propa               | MR to Reset Propagation Delay |                      |                                                                     |                    | 2                    |                     | μS     |

| MR Pull-up Resistance           |                               | $R_{\overline{MR}}$  |                                                                     |                    | 20                   |                     | kΩ     |

| Reset Timeout Period            |                               | too                  | C <sub>CT</sub> = 1500pF                                            | 3.35               | 4.375                | 5.40                | ms     |

|                                 |                               | t <sub>RP</sub>      | C <sub>CT</sub> = 0pF                                               |                    | 0.275                |                     |        |

| CT Source Current               |                               | I <sub>RAMP</sub>    |                                                                     |                    | 240                  |                     | nA     |

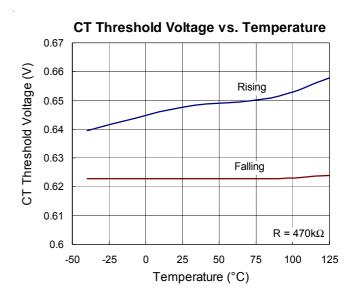

| CT Source Threshold Voltage     |                               | V <sub>TH-RAMP</sub> |                                                                     |                    | 0.65                 |                     | V      |

| CT Threshold Hysteresis         |                               |                      |                                                                     |                    | 33                   |                     | mV     |

- **Note 1.** Stresses listed as the above "Absolute Maximum Ratings" may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may remain possibility to affect device reliability.

- Note 2.  $\theta_{JA}$  is measured in natural convection at  $T_A$  = 25°C on a low effective thermal conductivity test board of JEDEC 51-3 thermal measurement standard.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

- Note 5. The voltage  $V_{OL}$  can be calculated by  $V_{OL} = V_{DD} I_r x R$ . Where R is the pull-up resistor and  $I_r$  is the current flowing through the pull-up resistor. For typical application R = 100k $\Omega$ , VOL is less than 0.2V.

DS9807-01 April 2011 www.richtek.com

# **Typical Operating Characteristics**

## **Application Information**

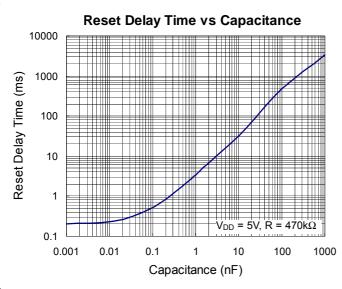

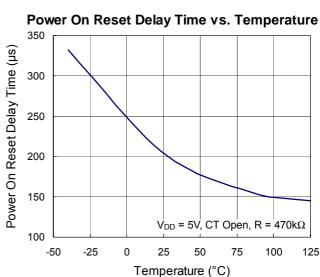

The RT9807 provides adjustable reset delay time to fit the need of a variety of  $\mu P$  applications. The reset delay time of the RT9807 can be adjusted by connecting a capacitor between the CT pin and GND. The CT capacitor must fit the need of low-leakage (<10nA), and it is recommended to use a ceramic capacitor such as X7R or NPO type.

#### **Reset Delay Time Setting**

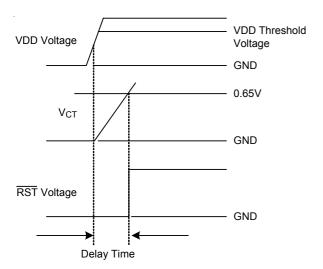

When the VDD voltage exceeds the VDD threshold voltage, a current source will start to charge the CT capacitor and the CT voltage will rise. When the CT voltage exceeds 0.65V, the  $\overline{\text{RST}}$  voltage will change from low to high. Therefore, there is a delay time between the point of VDD reaching its threshold voltage and the  $\overline{\text{RST}}$  active-high point. The delay time can be calculated according to the following equation.

tdelay (

$$\mu$$

s) =  $\frac{0.58}{0.18 \times 10^6 \text{ x Cct } (\mu\text{F})}$  + 220

Figure 1. Delay Time

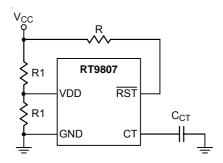

#### Operating with a Voltage Divider

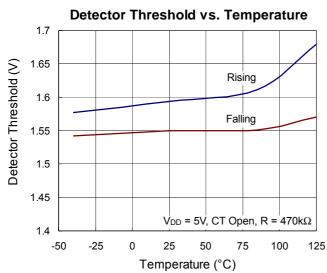

The voltage detector monitors the  $V_{\text{CC}}$  voltage to generate a reset signal when  $V_{\text{CC}}$  is higher than the detecting level. The detecting level is determined by an external resistive voltage divider.

VCC\_TH = VTH x

$$\left(1 + \frac{R1}{R2}\right)$$

, VTH : Threshold Voltage.

VCC\_HYS = VHYS x  $\left(1 + \frac{R1}{R2}\right)$

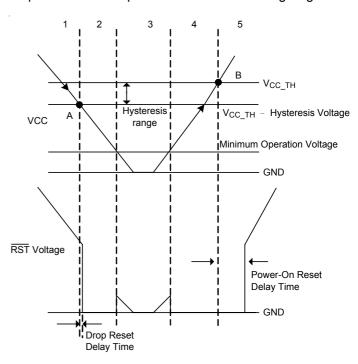

Figure 2. Voltage Divider

The rising and falling of the VCC and RST voltage can be explained in five steps as shown in the following diagram.

Figure 3. Operation Diagram

- 1. RST voltage is pulled up to VCC voltage.

- 2. When the VCC voltage is down to the detector threshold voltage (Point A), RST voltage becomes low level.

- 3. When the VCC voltage is lower than minimum operating voltage, the RST voltage is indefinite. In the case of open drain type, RST voltage is equal to pull-up voltage.

- 4. RST voltage becomes low level.

- 5. When the VCC voltage exceeds the threshold voltage (Point B), the internal source current will start to charge CT capacitor. The RST voltage will go high after a delay time when the CT capacitor voltage reaches 0.65V.

DS9807-01 April 2011 www.richtek.com

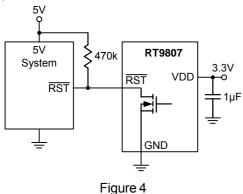

#### Interfacing to Other Voltages

The RT9807 is an open-drain voltage detector that can provide different voltage level of reset signals for processor application. As shown in Figure 4, the open-drain output can be connected to another voltage level less than 5.5V. This allows for easy logic compatibility to various microprocessors.

#### **Manual Reset Input**

Many processor based products require manual reset capability, allowing the user or external logic circuitry to initiate a reset. A logic low on MR asserts reset. Reset remains asserted while MR is low and for the reset timeout period after MR returns high. Connect a normally open momentary switch from MR to ground to create a manual reset function.

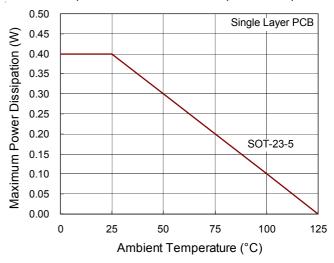

#### **Thermal Considerations**

For continuous operation, do not exceed absolute maximum operation junction temperature. The maximum power dissipation depends on the thermal resistance of IC package, PCB layout, the rate of surroundings airflow and temperature difference between junction to ambient. The maximum power dissipation can be calculated by following formula:

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$$

where  $T_{J(MAX)}$  is the maximum operation junction temperature,  $T_A$  is the ambient temperature and the  $\theta_{JA}$  is the junction to ambient thermal resistance.

For recommended operating conditions specification of the RT9807, the maximum junction temperature is 125°C. The junction to ambient thermal resistance  $\theta_{JA}$  is layout dependent. For SOT-23-5 package, the thermal resistance  $\theta_{JA}$  is 250°C/W on the standard JEDEC 51-3 single layer thermal test board. The maximum power dissipation at

$T_A = 25^{\circ}$ C can be calculated by the following formula :

$$P_{D(MAX)}$$

= (125°C  $-$  25°C) / (250°C/W) = 0.4W for SOT-23-5 package

The maximum power dissipation depends on operating ambient temperature for fixed  $T_{J(MAX)}$  and thermal resistance  $\theta_{JA}$ . For RT9807 package, the derating curve in Figure 5 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 5. Derating Curve for RT9807 Package

#### **Layout Considerations**

CT is a precise current source. When developing the layout for the application, be careful to minimize board capacitance and leakage currents around this pin.

Traces connected to CT should be kept as short as possible. Traces carrying high-speed digital signals and traces with large voltage potentials should be routed as far from CT as possible. Leakage current and stray capacitance (e.g., a scope probe) at this pin can cause errors in the reset delay time.

Figure 6. PCB Layout Guide

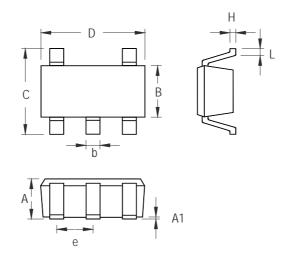

### **Outline Dimension**

| Cumbal | Dimensions | In Millimeters | Dimensions In Inches |       |  |

|--------|------------|----------------|----------------------|-------|--|

| Symbol | Min        | Max            | Min                  | Max   |  |

| Α      | 0.889      | 1.295          | 0.035                | 0.051 |  |

| A1     | 0.000      | 0.152          | 0.000                | 0.006 |  |

| В      | 1.397      | 1.803          | 0.055                | 0.071 |  |

| b      | 0.356      | 0.559          | 0.014                | 0.022 |  |

| С      | 2.591      | 2.997          | 0.102                | 0.118 |  |

| D      | 2.692      | 3.099          | 0.106                | 0.122 |  |

| е      | 0.838      | 1.041          | 0.033                | 0.041 |  |

| Н      | 0.080      | 0.254          | 0.003                | 0.010 |  |

| L      | 0.300      | 0.610          | 0.012                | 0.024 |  |

**SOT-23-5 Surface Mount Package**

### **Richtek Technology Corporation**

Headquarter

5F, No. 20, Taiyuen Street, Chupei City

Hsinchu, Taiwan, R.O.C.

Tel: (8863)5526789 Fax: (8863)5526611

### **Richtek Technology Corporation**

Taipei Office (Marketing)

5F, No. 95, Minchiuan Road, Hsintien City

Taipei County, Taiwan, R.O.C.

Tel: (8862)86672399 Fax: (8862)86672377

Email: marketing@richtek.com

Information that is provided by Richtek Technology Corporation is believed to be accurate and reliable. Richtek reserves the right to make any change in circuit design, specification or other related things if necessary without notice at any time. No third party intellectual property infringement of the applications should be guaranteed by users when integrating Richtek products into any application. No legal responsibility for any said applications is assumed by Richtek.

DS9807-01 April 2011 www.richtek.com